【www.zhangdahai.com--教学设计】

打开文本图片集

摘要:卫星导航信号源是卫星导航接收机研制过程中的重要测试设备。采用软件无线电技术,实现了一种基于DSP+FPGA的多通道GPS中频信号源。基于GPS中频信号数学模型,给出了系统整体设计方案。采用模块化设计,详细阐述了DSP与FPGA的数据交互逻辑、总线接口模块、载波NCO模块、码模块和导航电文缓冲模块等系统关键部分的实现及重要参数设置的依据,并给出ModelSim-Mtera 6.4a下各模块的仿真结果。实测结果表明,信号源生成中频信号波形、频谱符合GPS信号体制规范,且能够被软件接收机正确捕获、跟踪。该信号源具有良好的实时性和可扩展性,成本可控,可有效应用于实验室环境下接收机的性能测试。

关键词:GPS信号源;多通道;数字信号处理器;现场可编程门阵列

文献标识码:A 文章编号:1674-5124(2016)11-0100-07

0 引言

卫星导航信号源是卫星导航研究领域的重要设备,利用它可以在实验室环境下对卫星导航接收机的捕获、跟踪性能进行有效的测试与评估,尤其是对于高动态等复杂场景,可大大减少接收机设备的研制成本。

目前国内外研制的卫星导航信号源主要有3种类型:软件信号源、采集回放式信号源和硬件信号源。软件信号源主要基于Matlab/Simulink、VisualC++等软件开发平台实现,信号参数计算和调制生成均由软件完成。该方式生成信号精度较高,易于实现,成本较低,但使用时需提前生成信号,不能实时应用,且占用大量存储空间。采集回放式信号源使用时首先采集实际导航信号并存储,然后在需要时回放已存信号。该方式能够产生真实环境的导航信号,硬件结构相对简单,开发复杂度低,但是只能产生已采集的信号,灵活性较差。硬件信号源一般由上位机软件和专用信号产生板卡构成,信号参数计算由上位机软件完成,信号调制生成则由硬件板卡实现。该类信号源多采用VXI、CPCI或PXI等高速总线架构,精度高,能够实时工作,但技术复杂,实现难度大。目前硬件信号源多由国外进口,核心技术被国外垄断,且功能严格受限,价格昂贵,一般高校实验室或科研院所难以承受。因此,研制具有自主知识产权的硬件信号源具有重要意义。

本文采用软件无线电技术,实现了一种基于DSP+FPGA的多通道GPS中频信号源。结合DSP计算性能强大和FPGA善于并行处理的特点,将主要信号参数的计算放在DSP中完成,FPGA则进行多路数字中频信号的调制与生成,精度高,实时性好,成本可控;充分利用器件的可编程特性,减少外围芯片数量,降低硬件设计复杂度;采用模块化设计,使系统易于维护和升级。理论分析与测试表明,该中频信号源达到伪距变化率误差±0.01m/s、伪距误差±0.01m的系统设计指标,生成信号波形、频谱符合GPS信号体制规范,能够用于接收机捕获、跟踪测试。

1 GPS中频信号的数学模型

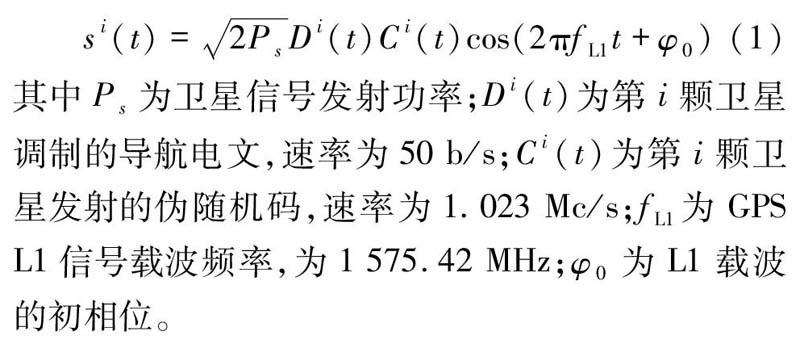

GPS系统从本质上讲,是一个基于码分多址(CDMA)的无线扩频通信系统。对于GPS L1频点C/A码信号,第i颗卫星在t时刻(GPS系统时)所发射的信号si(t)可表示成:

(1)其中P,为卫星信号发射功率;Di(t)为第i颗卫星调制的导航电文,速率为50 b/s;Ci()为第i颗卫星发射的伪随机码,速率为1.023 Mc/s;fL1为GPSL1信号载波频率,为1 575.42 MHz;φ0为L1载波的初相位。

多顆卫星的信号经过一段时间的传播后到达接收机射频前端,经过多级下变频和带通滤波后的合成中频信号可表示为

(2)其中,i为可见卫星的PRN号;Pir为卫星信号接收功率;fIF为经下变频后的中频信号频率,为4.309MHz;τi为信号从卫星传输到地面的总延迟;fid为接收机与卫星间的相对运动引起的信号多普勒频移。

本设计采用数字化信号生成方法,将式(2)数字化可得:

(3)其中Ts为信号采样间隔。

GPS中频信号源,是根据式(3)产生包含载体动态特性的GPS中频信号。

2 系统设计方案

多通道GPS中频信号源系统的结构框图如图1所示。系统由数字中频信号产生部分和外围模块两大部分构成。数字中频信号产生部分采用DSP+FPGA的软件无线电架构设计方案,其中DSP选用TI公司TMS320C6713B芯片,FPGA选用Mtera公司Stratix Ⅱ系列EP2S60F48414芯片;外围模块主要包括上位机软件部分和DA转换模块AD9777。

信号源中,DSP芯片是数字中频信号产生部分的核心部件,它完成整个信号源硬件平台的初始化和控制。DSP同时承担了信号源大部分的参数计算工作,具体来讲,对应到式(3),主要有:可见卫星PRN号i,导航电文Di(nTs),信号传播总延迟τi和信号多普勒频移fid。其中延迟和多普勒参数的计算是信号源实现对伪距和接收机动态模拟的核心。DSP通过计算这两个参数,并将其转化为初始码片计数、码频率控制字、码相位调整字,载波频率控制字、载波相位调整字,控制FPGA产生所需状态的信号。

FPGA在DSP的控制下,产生GPS数字中频信号。对应到式(3),FPGA的功能主要有:各通道伪随机码Ci(nTs)、数字中频载波cos(2πfIEnTs+φ0)的产生;接收DSP发送的导航电文和频率控制字、相位调整字等控制参数;根据收到的控制参数,通过数字控制振荡器(numerically controlled oscillator,NCO)实现对码和载波的频率及相位的控制,以实现对GPS信号的传输延迟及多普勒效应的模拟;实现数据码的扩频调制以及载波的BPSK调制;实现多通道信号的合成。

此外,在FPGA内部还设计了串口收发模块,实现上位机与DSP交互数据的缓存和转发,以减少系统外围芯片的数量。

3 系统关键模块实现

由式(3)可知,GPS数字中频信号是多颗卫星中频信号的叠加。信号源首先并行产生各颗可见卫星的中频信号,再将多个通道的信号叠加输出。每个信号产生通道在FPGA中实现的方法一样。总线接口模块及信号产生通道结构框图如2所示。

3.1 DSP与FPGA的接口及数据交互

信号源在初始化和运行时,DSP与FPGA之间有频繁的数据交互,需采用可靠的设计以保证数据传输的可靠性和实时性。本设计中,FPGA作为一个片外存储器外设连接在DSP的外部存储器接口(external memory interface,EMIF),并通过产生外部中断控制DSP对FPGA的读写操作,二者构成一个基于中断驱动的实时系统。

如图2所示,FPGA连接在DSPEMIF的CE2空间,EMIF相应空间配置为“32位异步接口”模式。FPGA内部逻辑产生1ms周期性脉冲,输出至DSP外部中断4号引脚,触发DSP中断,控制二者的数据交互。

DSP在进入中断后,将计算完成的实时码、载波控制字传输至FPGA,以控制生成信号的状态。同时DSP将读取FPGA导航电文读空标识状态,若该值为1,表示需要更新导航电文,DSP将发送新的导航电文至FPGA(以字(30 bit)为单位,每次发送4字)。

除此之外,DSP在每次进入中断后会读取码NCO和载波NCO累加的实时码相位、载波相位值,用于控制字的校正。同时,在每个中断周期间,DSP需完成伪距的实时计算,并将其转换为码、载波控制字,在中断服务程序中发送至FPGA。

3.2 总线接口模块

在FPGA中,总线接口模块实现了相关寄存器及其地址的定义。DSP写入FPGA的数据,根据不同地址缓存至相应寄存器,进而被信号产生通道各模块读取。

对于32位异步存储访问,EMIF可用外部地址总线为EA[21:2],相应FPGA定义的寄存器地址访问规则为:将20位地址线分为两部分,EA[21:18]用于读写译码,“4’b0001”表示对FPGA进行写操作,“4"b0010”表示对FPGA进行读操作;EA[17:2]用于寄存器地址译码。寄存器地址由3部分组成:系统段基址+通道段基址+寄存器偏移地址。FPGA中信号产生通道相关寄存器地址定义如表1所示,其中变量i表示通道号,取值范围为1~12。

3.3 载波NCO模块

载波NC0模块接收DSP送来的载波频率控制字FW_CARR_NC0、载波相位调整字PW_CARR_NCO,实现动态数字中频载波的产生。载波NC0基于直接数字频率合成器(direct digital synthesizer,DDS)原理实现,其结构如图3所示。

如图所示,载波NCO主要由加法器、32位寄存器和波形查找表ROM构成。其中为节省存储空间,截取当前相位累加值的高10位作为波形查找表ROM读地址。波形查找表实现载波相位至幅度的转换,查找表中载波幅度值量化为12 bit。

由DDS原理可知,当系统时钟频率为fclock,累加寄存器位宽为Ⅳ,频率控制字为FW_CARR_NC0时,输出信號频率fout为:

(4)

频率分辨率△f为:

(5)

同时,为了模拟信号的传输延迟引起的载波相位变化,设置了相位调整字PW_CARR_NC0。相位变化量△φ与相位调整字PW_CARR_NC0的关系为:

(6)

由式(5)可知,累加寄存器位宽N与频率分辨率△f等系统指标密切相关。根据系统设计指标,伪距变化率误差为vres=±0.01 m/s,则对于L1载波频点,要求多普勒模拟精度为:

(7)

因此,载波NCO频率分辨率需满足:△f≤△fd。本设计中,系统时钟为150 MHz,根据式(5),可得累加寄存器位宽N为:

(8)式中[x]表示向上取整。因此,本设计中载波NC0累加寄存器位宽设为32位。

当输出中频载波频率为4.309 MHz时,根据式(4)计算可得频率控制字FW_CARR_NCO为0x75AA17E。载波NC0模块仿真结果(仿真环境为ModelSim-Mtera 6.4a,下同)如图4所示。

3.4 码模块

码模块由码NCO和码产生模块两部分构成。与载波NCO类似,码NCO模块也是在DSP发送来的码频率控制字FW_CODE_NCO和码相位调整字PW_CODE_NCO的控制下,产生频率和相位可调的码时钟。不同的是码NCO的输出作为码产生模块的使能时钟,仅输出“0”、“1”即可,不需要进行相位截断,也不需要波形查找表。码NCO结构如图5所示。

码NCO累加寄存器位宽M与系统伪距模拟精度△ρ的关系为:

(9)式中Tcode为C/A码码元宽度。

根据系统设计指标,C/A码伪距误差为ρres=±0.01 m,即要求伪距模拟精度:△ρ≤|ρres|。根据式(9),可得累加寄存器位宽M为:

(10)

本设计中,取码NCO累加寄存器位宽与载波NCO相同,为32 bit,使二者在同一系统时钟下具有相同的频率分辨率,且能充分保证伪距模拟精度的要求。

GPS信号中的C/A码是一种Gold码,它由两个10位的线性反馈移位寄存器G1和G2产生的优选m序列对异或相加而成。本设计采用赋初值法实现码产生模块,即移位寄存器G1初值均设为10’h3FF,通过给移位寄存器G2赋不同初值,产生不同卫星的码序列。

码模块整体仿真结果如图6所示,仿真产生2号卫星C/A码,码速率设为1.023MHz。PRN_SEL为卫星号控制字,用于设置G2寄存器初值,此处设为0x6F,对应2号卫星;系统时钟clock为150MHz,带入式(4)计算可得频率控制字FW_CODE_NCO为0x1BEF49D;PW_CODE_NCO为码相位调整字,CODE_DEL_CNT为码片延迟计数,分别用于调整码片内相位和码周期内相位,此处均设为0;fclock为码时钟,CA_CODE_OUT为码序列输出。

3.5 导航电文缓冲模块

GPS信号源中,导航电文由DSP计算产生并按电文帧格式组织后发送至FPGA进行扩频调制。由于DSP向FPGA写入导航电文是通过EMIF总线以EMIF输出时钟ECLKOUT速率(50MHz)进行,为高速并行方式;而FPGA信号调制模块读取导航电文进行调制是按比特以导航电文速率(50Hz)进行,为低速串行方式。二者属于跨时钟域异步通信,且需进行数据并行至串行传输的转换,因此设计单独的导航电文缓冲模块解决上述两个问题。

解决跨时钟域数据传输可靠性问题的方法主要有单向控制信号检测、专用握手信号和借助于存储器。由于FPGA内部提供丰富的存储器资源,本设计中采用双时钟FIFO(DCFIFO)作为数据缓存单元,解决这一问题。同时,为完成数据传输的并串转换,采用了带有同步并行预置数功能的移位寄存器实现这一功能。

此外,为保证导航电文连续、可靠的传输,避免电文更新时的等待,实现数据的无缝缓冲与处理,本设计采用两个DCFIFO构成乒乓结构,通过设计专门的输入输出选择模块,控制两个DCFIFO交替地进行读写。导航电文缓冲模块的结构如图7所示。

导航电文缓冲模块中,DCFIFO和并串转换移位寄存器均利用Ahera Megafunction宏功能实现。两个DCFIFO的大小均为30bits×4words,移位寄存器长度同为30bit。仿真开始前,DSP首先向DCFIFO_1写入4字的电文数据;等检测到rdempty_2&wrfull_1(rdempty_x和wrfull_x分别为DCFIFO_x读空和写满信号,下同)信号变为高电平时开始从DCFIFO_1读取电文数据至并串转换器,与此同时,DSP开始向DCFIFO_2写入新的4字电文数据;等检测到rdempty_1&wrfull_2信号变为高电平时切换DCFIFO_1和DCFIFO_2的读写;以后读写在两个DCFIFO间依次交替进行。导航电文缓冲模块能够正确实现數据无缝缓冲和并串转换的功能。

4 系统测试

4.1 中频信号波形及频谱

分别将程序通过仿真器下载至DSP和FPGA,并使用在线逻辑分析仪SignalTap Ⅱ采集信号源产生的中频信号,观察其时域波形;并将数据导入到Matlab观察其频谱,验证其是否符合GPS信号体制规范。以产生的GPS 2号卫星中频信号为例,图8、9分别显示了其时域、频域波形。图8显示在某些时刻,载波信号相位反相,符合BPSK信号特性;图9显示生成信号的中心频率约为4.309 MHz,主瓣带宽约为2 MHz,与GPS C/A码信号特性一致。

4.2 软件接收机捕获及跟踪测试结果

设置信号源产生GPS 1、2、18及23号卫星的中频合路信号,并将产生的中频信号保存为二进制文件,仿照GP2015射频前端输出数据格式的要求对中频信号进行带通采样(采样率5.714 MHz),然后将数据导人到Matlab软件接收机进行捕获、跟踪测试。图10显示了软件接收机捕获到的各颗卫星,与预期一致。

图11分别显示了2号卫星的捕获、跟踪结果。如图所示,中频数据导入Matlab软件接收机后,可以被正确捕获、跟踪并解调导航电文。

结合4.1GPS中频信号时、频域分析的结果,可认为所设计的GPS中频信号源能够正确产生所需的GPS中频信号。

5 结束语

本文根据GPS中频信号数学模型,设计并实现一种基于DSP+FPGA架构的多通道GPS中频信号源。给出信号源整体设计方案,并重点介绍DSP与FPGA的接口及数据交互逻辑设计,总线接口模块、载波NCO模块、码模块和导航电文缓冲模块的实现原理和关键参数设置的依据,以及各模块仿真结果。理论分析和测试结果表明,设计的信号源达到伪距变化率误差±0.01 m/s、伪距误差±0.01 m的系统设计指标,并能用于软件接收机捕获、跟踪测试。

(编辑:刘杨)

本文来源:http://www.zhangdahai.com/jiaoxueziyuan/jiaoxuesheji/2023/0402/578830.html